Manual de Arty de Digilent

- 1 Descripción general

- 2 Diseño con Arty

- 3 Fuentes de alimentación

- 4 Configuración de la FPGA

- 5 Memoria

- 6 Ethernet PHY

- 7 Osciladores/Relojes

- 8 Puente USB-UART (Puerto serie)

- 9 E/S básicas

- 10 Conectores Pmod

- 11 Conector de shield Arduino/chipKIT

- 12 Referencias

- 13 Descargar el manual

- 14 En otros idiomas

Descripción general

Arty es una plataforma de desarrollo lista para usar diseñada en torno al Field Programmable Gate Array (FPGA) Artix-7 de Xilinx. Se diseñó específicamente para su uso como un sistema de procesamiento suave MicroBlaze. Cuando se usa en este contexto, Arty se convierte en la plataforma de procesamiento más flexible que se podría agregar a su colección, capaz de adaptarse a lo que requiera su proyecto. A diferencia de otras Single Board Computers, Arty no está ligada a un único conjunto de periféricos de procesamiento: En un momento es una potencia repleta de UARTS, SPIs, IICs y un Ethernet MAC, y al siguiente es un meticuloso cronometrador con una docena de temporizadores de 32 bits.

- FPGA Xilinx Artix-35T (xc7a35ticsg324-1L)

- 33 280 celdas lógicas en 5200 slices (cada slice contiene cuatro LUT de 6 entradas y 8 flip-flops);

- 1800 Kbits de RAM de bloque rápido;

- Cinco módulos de gestión de reloj, cada uno con un bucle de enganche de fase (PLL);

- 90 slices DSP;

- Velocidades de reloj internas superiores a 450 MHz;

- Convertidor analógico a digital en chip (XADC).

- Programable mediante JTAG y Quad-SPI Flash

- Características del sistema

- 256 MB DDR3L con un bus de 16 bits a 667 MHz

- 16 MB de Quad-SPI Flash

- Circuitos de programación USB-JTAG

- Alimentado por USB o cualquier fuente de 7 V-15 V

- Conectividad del sistema

- Ethernet de 10/100 Mbps

- Puente USB-UART

- Dispositivos sensoriales y de interacción

- 4 interruptores

- 4 botones

- 1 botón de reinicio

- 4 LED

- 4 LED RGB

- Conectores de expansión

- 4 conectores Pmod

- Conector de shield Arduino/chipKIT

Arty es totalmente compatible con la suite de diseño Vivado ® de alto rendimiento. Se admite bajo la licencia gratuita WebPACK™, por lo que los diseños se pueden implementar sin coste adicional. Esta licencia gratuita incluye la capacidad de crear diseños de procesador de núcleo blando MicroBlaze™. Los recursos de diseño, los proyectos de ejemplo y los tutoriales están disponibles para su descarga en el Arty Resource Center, accesible desde reference.digilentinc.com.

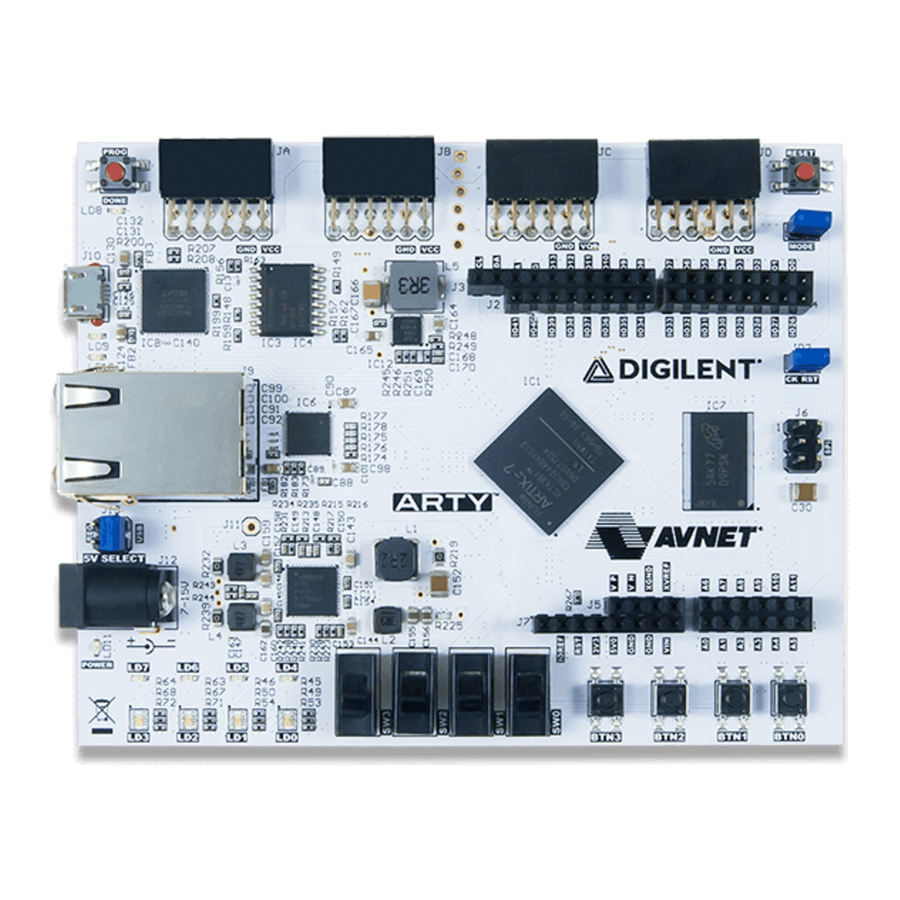

| Indicación | Descripción |

| 1 | LED DONE de programación FPGA |

| 2 | Puerto USB JTAG/UART compartido |

| 3 | Conector Ethernet |

| 4 | Jumper de selección de alimentación (Suministro externo/USB) |

| 5 | Conector de alimentación (para suministro externo opcional) |

| 6 | LED de alimentación correcta |

| 7 | LED de usuario |

| 8 | Interruptores deslizantes de usuario |

| 9 | Pulsadores de usuario |

| 10 | Conectores de shield Arduino/chipKIT |

| 11 | Cabecera SPI (compatible con Arduino/chipKIT) |

| 12 | Jumper de reinicio del procesador chipKIT |

| 13 | Modo de programación FPGA (JTAG/Flash) |

| 14 | Reinicio del procesador chipKIT |

| 15 | Cabeceras Pmod |

| 16 | Botón de reinicio de programación FPGA |

| 17 | Flash SPI |

| 18 | FPGA Artix |

| 19 | Memoria Micron DDR3 |

| 20 | Fuente de alimentación ADP 5052 de Analog devices |

Tabla 1. Descripciones de las indicaciones de hardware de Arty.

Diseño con Arty

Lo que hace que Arty sea tan flexible es su FPGA. Entre sus muchas características, las FPGA tienen la capacidad de transformarse en un System-on-a-Chip (SoC) definido por software personalizado. Estas configuraciones FPGA "Soft SoC" se diseñan gráficamente utilizando una herramienta llamada Vivado IP Integrator (Vivado IPI). En esta herramienta, los bloques periféricos preconstruidos se arrastran desde una extensa biblioteca y se colocan en su sistema de procesamiento según le convenga. Estos periféricos preconstruidos incluyen temporizadores, controladores UART/SPI/IIC y muchos de los otros dispositivos que normalmente encontraría en un SoC o

microcontrolador. Los usuarios ambiciosos también encontrarán que pueden crear sus propios bloques periféricos escribiéndolos en un lenguaje de definición de hardware (HDL), específicamente Verilog o VHDL. Para aquellos que no estén interesados en aprender HDL, la herramienta Xilinx High Level Synthesis se puede utilizar para definir bloques periféricos personalizados escribiéndolos en C.

Las configuraciones Soft SoC de Arty están impulsadas por núcleos de procesador MicroBlaze. MicroBlaze es un núcleo de procesador blando RISC de 32 bits, diseñado específicamente para ser utilizado en FPGA de Xilinx. El procesador MicroBlaze en una configuración Arty SoC se ejecuta normalmente a 100 MHz, aunque es posible diseñar su SoC para que pueda operar a más de 200 MHz. Arty admite grandes programas MicroBlaze con exigentes requisitos de memoria al proporcionar 16 MB de memoria de programa no volátil y 256 MB de RAM DDR3L.

Después de diseñar su configuración Soft SoC para Arty, puede comenzar a escribir programas para ella. Esto se hace exportando su diseño SoC fuera de Vivado IPI y al Xilinx Software Development Kit (XSDK), un entorno de desarrollo integrado (IDE) para diseñar/depurar programas MicroBlaze en C. Después de la transferencia de IPI a XSDK, XSDK se configura automáticamente para incluir bibliotecas y ejemplos para los bloques periféricos que ha incluido en su SoC. En este punto, la programación de Arty es muy similar a la programación de otras plataformas SoC o microcontroladores: Los programas se escriben en C, se programan en la placa a través de USB y luego se depuran opcionalmente en hardware. Las configuraciones Soft SoC y los programas MicroBlaze también se pueden cargar en la memoria de programa no volátil de 16 MB para que se ejecuten inmediatamente después de encender Arty.

Aunque Arty es particularmente adecuado para diseños MicroBlaze Soft SoC, también se puede programar con una descripción de circuito de nivel de transferencia de registro (RTL) como cualquier otra plataforma de desarrollo FPGA. Este flujo de diseño requiere que describa su circuito RTL utilizando un HDL dentro de Vivado, y no utiliza las herramientas Vivado IPI o XSDK. Diseñar de esta manera tiene muchas ventajas, pero es muy diferente a programar un solo ordenador de placa, y en su lugar es utilizado por aquellos que están familiarizados con el diseño FPGA o interesados en diseñar e implementar un circuito digital que no contiene un procesador.

Fuentes de alimentación

La placa Arty requiere una fuente de alimentación de 5 V para funcionar. Esta fuente de alimentación puede provenir del puerto USB-JTAG de Digilent (J10) o puede derivarse de una fuente de alimentación de CC de 7 a 15 voltios que esté conectada al conector de alimentación (J12) o al pin 8 de la cabecera J7. La cabecera J13, ubicada entre el conector de alimentación y el conector Ethernet, se utiliza para determinar qué fuente se utiliza.

Un LED de alimentación correcta (LD11), impulsado por la salida "power good" (PWRGD) del regulador ADP5052, indica que la placa está recibiendo alimentación y que los suministros integrados están funcionando como se espera. A continuación, se muestra una descripción general del circuito de alimentación de Arty.

El puerto USB puede suministrar suficiente energía para la gran mayoría de los diseños. Sin embargo, algunas aplicaciones exigentes, incluyendo cualquiera que impulse múltiples placas periféricas, podrían requerir más energía de la que puede proporcionar el puerto USB. Además, algunas aplicaciones pueden necesitar ejecutarse sin estar conectadas al puerto USB de un PC. En estos casos, se puede utilizar una fuente de alimentación externa o una batería.

Se puede utilizar una fuente de alimentación externa conectándola al conector de alimentación J12 e instalando un jumper en la posición "REG" en la cabecera J13. La fuente debe utilizar un enchufe coaxial, con centro positivo de 2,1 mm (o 2,5 mm) de diámetro interno, y proporcionar un voltaje de 7 a 15 voltios de CC. La fuente debe proporcionar una corriente mínima de 1 amperio. Idealmente, la fuente debe ser capaz de proporcionar 36 vatios de potencia (12 voltios de CC, 3 amperios).

Se puede utilizar una batería externa conectando el terminal positivo de la batería al pin 8 de J7 (etiquetado como VIN) y el terminal negativo al pin 7 de J7 (etiquetado como GND), como se muestra en la figura siguiente. Para utilizar la batería como fuente de alimentación de la placa, se debe instalar un jumper en la posición "REG" en la cabecera J13. La batería debe proporcionar un voltaje entre 7 y 15 voltios de CC, y NO debe instalarse mientras haya una fuente conectada al conector de alimentación J12.

Los circuitos reguladores de voltaje de Analog Devices y Texas Instruments crean los suministros requeridos de 3,3 V, 1,8 V, 1,35 V, 1,25 V y 0,95 V a partir de la fuente de alimentación de 5 V. En el caso de que se utilice una fuente de alimentación externa o una batería, el regulador de 5 V de Analog Devices integrado proporciona la fuente de 5 V. La siguiente tabla proporciona información adicional (las corrientes típicas dependen en gran medida de la configuración de la FPGA y los valores proporcionados son típicos de los diseños de tamaño/velocidad medios).

| Suministro | Circuitos | Dispositivo | Corriente (máx./típica) |

| 5V | Reguladores integrados, LED RGB | IC12: Analog Devices ADP2384 | 3,5 A/0,375 A a 2 A |

| 3.3V | E/S de FPGA, relojes, flash, Pmods, LED, botones, interruptores, puerto USB, Ethernet | IC11: Analog Devices ADP5052 | 2,2 A/NA |

| 0.95V | FPGA Core y Block RAM | IC11: Analog Devices ADP5052 | 1,0 A/0,2 A a 0,8 A |

| 1.8V | Auxiliar de FPGA | IC11: Analog Devices ADP5052 | 1,0 A/NA |

| 1.35V | DDR3L y banco FPGA asociado | IC11: Analog Devices ADP5052 IC13: Texas Instruments | 1,0 A/NA |

| 1.25V | Referencia analógica XADC | IC13: Texas Instruments REF3012 | 25 mA/NA |

Tabla 2. Información del circuito regulador de voltaje.

Monitoreo de voltaje de suministro externo

La placa Arty incluye circuitos para monitorear el voltaje de un suministro externo conectado al conector de alimentación J12, o una batería externa conectada a la cabecera J7. Se utiliza un divisor de voltaje para escalar el voltaje de entrada no regulado, VU, para que esté dentro del rango (0-1V) que el ADC de 12 bits en chip es capaz de medir. El voltaje de entrada no regulado, VU, se divide por 16 y luego se alimenta al canal auxiliar 2 en el XADC del Artix 35T. Las aplicaciones que deseen monitorear el voltaje de un suministro externo pueden configurar el canal 2 del XADC como una entrada unipolar y realizar una conversión para recibir un valor digital correspondiente al voltaje de entrada. La siguiente figura proporciona una descripción general que permite monitorear un voltaje de suministro externo.

Monitoreo de corriente de suministro de núcleo FPGA

La placa Arty incluye circuitos para monitorear la corriente consumida por el núcleo FPGA. La corriente se monitorea midiendo el voltaje a través de una resistencia de detección de 10 miliohmios que se coloca entre la salida del regulador de conmutación de 0,95 V (IC11, canal 2) y la red VCC0V95. Un amplificador de detección de corriente (IC15, INA199A1 de Texas

Instrument) conectado a través de la resistencia de detección proporciona una ganancia de 50 y produce un voltaje de salida de 500 milivoltios por amperio de corriente. La salida del amplificador de detección de corriente se alimenta al canal auxiliar 10 en el XADC del Artix 35T. Las aplicaciones que deseen monitorear el consumo de corriente del FPGA Core y Block RAM pueden configurar el canal 10 del XADC como una entrada unipolar y realizar una conversión para recibir un valor digital que corresponda al voltaje amplificado de la resistencia de detección. La siguiente figura proporciona una descripción general de los circuitos que permiten monitorear la corriente de suministro del núcleo FPGA.

Monitoreo de alimentación de suministro de 5 V

La placa Arty incluye circuitos para monitorear el voltaje del suministro de 5 voltios, así como la corriente consumida por este suministro. Se utiliza un divisor de voltaje para escalar el voltaje de entrada de 5 V para que esté dentro del rango (0-1V) que el ADC de 12 bits en chip es capaz de medir. El voltaje de suministro de 5 V se divide por 5,99 y luego se alimenta al canal auxiliar 1 en el XADC del Artix 35T. Se utiliza una combinación de una resistencia de detección de corriente de 5 miliohmios y un amplificador de detección de corriente (IC14, Texas Instruments INA199A1) para producir un voltaje de salida de 250 milivoltios por amperio de corriente. La salida del amplificador de detección de corriente se alimenta al canal auxiliar 9 en el XADC del Artix 35T. Las aplicaciones que deseen monitorear el consumo de energía instantáneo de la placa Arty pueden configurar los canales 1 y 9 del XADC como entradas unipolares y luego realizar una conversión simultánea de los dos canales para recibir valores digitales que se pueden utilizar para calcular el consumo de energía instantáneo. La siguiente figura proporciona una descripción general de los circuitos que permiten monitorear el consumo de energía del suministro de 5 V.

Configuración de la FPGA

Después del encendido, la FPGA Artix-7 debe configurarse (o programarse) antes de que pueda realizar cualquier función. Puede configurar la FPGA de una de estas dos maneras:

- Un PC puede usar el circuito Digilent USB-JTAG (puerto J10) para programar la FPGA en cualquier momento en que esté encendida.

- Se puede transferir un archivo almacenado en el dispositivo flash serial no volátil (SPI) a la FPGA usando el puerto SPI.

![Digilent - Arty - Configuración de la FPGA Configuración de la FPGA]()

La Figura 3 muestra las diferentes opciones disponibles para configurar la FPGA. Un puente "mode" (modo) integrado (JP1) selecciona si la FPGA se programará mediante la flash Quad-SPI al encenderse.

Los datos de configuración de la FPGA se almacenan en archivos llamados bitstreams que tienen la extensión de archivo .bit. El software ISE o Vivado de Xilinx puede crear bitstreams a partir de archivos de origen basados en VHDL, Verilog o esquemas (en el conjunto de herramientas ISE, EDK se usa para diseños basados en procesadores integrados MicroBlaze).

Los bitstreams se almacenan en celdas de memoria volátil dentro de la FPGA. Estos datos definen las funciones lógicas y las conexiones de circuito de la FPGA, y siguen siendo válidos hasta que se borran quitando la alimentación de la placa, presionando el botón de reinicio conectado a la entrada PROG o escribiendo un nuevo archivo de configuración usando el puerto JTAG.

Un bitstream de Artix-7 35T suele ser de 17.536.096 bits. El tiempo que se tarda en programar la Arty se puede reducir comprimiendo el bitstream antes de la programación y luego permitiendo que la propia FPGA descomprima el bitstream durante la configuración. Dependiendo de la complejidad del diseño, se pueden lograr relaciones de compresión de 10x. La compresión de bitstream se puede habilitar dentro de las herramientas de Xilinx (ISE o Vivado) para que se produzca durante la generación. Para obtener instrucciones sobre cómo hacerlo, consulte la documentación de Xilinx para el conjunto de herramientas que se esté utilizando.

Después de programarse correctamente, la FPGA hará que se ilumine el LED "DONE" (HECHO). Presionar el botón "PROG" (PROG) en cualquier momento restablecerá la memoria de configuración en la FPGA. Después de restablecerse, la FPGA intentará inmediatamente reprogramarse a sí misma desde cualquier método que haya sido seleccionado por los puentes del modo de programación.

Las siguientes secciones proporcionan mayor detalle sobre la programación de la Arty usando los diferentes métodos disponibles.

Configuración JTAG

Las herramientas de Xilinx suelen comunicarse con las FPGA usando el Test Access Port and Boundary-Scan Architecture, comúnmente conocido como JTAG. Durante la programación JTAG, un archivo .bit se transfiere desde el PC a la FPGA usando el circuito Digilent USB-JTAG integrado (puerto J10) o un programador JTAG externo, como el Digilent JTAG-HS2, conectado al puerto J8. Puede realizar la programación JTAG en cualquier momento después de que la Arty se haya encendido, independientemente de si el puente de modo (JP1) está configurado. Si la FPGA ya está configurada, la configuración existente se sobrescribe con el bitstream que se transmite a través de JTAG. No configurar el puente de modo (que se ve en la Figura 3) es útil para evitar que la FPGA se configure desde la flash Quad-SPI hasta que se produzca una programación JTAG.

La programación de la Arty con un bitstream sin comprimir usando el circuito USB-JTAG integrado suele tardar alrededor de 6 segundos. La programación JTAG se puede realizar usando el administrador de hardware en Vivado o la herramienta iMPACT incluida con ISE.

Configuración Quad-SPI

Dado que la memoria de la FPGA en la Arty es volátil, depende de la memoria flash Quad-SPI para almacenar la configuración entre ciclos de energía. Este modo de configuración se llama Master SPI. La FPGA en blanco asume el rol de maestro y lee el archivo de configuración del dispositivo flash al encenderse. A tal efecto, primero es necesario descargar un archivo de configuración a la flash. Al programar un dispositivo flash no volátil, un archivo bitstream se transfiere a la flash en un proceso de dos pasos. Primero, la FPGA se programa con un circuito que puede programar dispositivos flash, y luego los datos se transfieren al dispositivo flash a través del circuito FPGA (esta complejidad está oculta al usuario por las herramientas de Xilinx). Esto se llama programación indirecta. Una vez que el dispositivo flash ha sido programado, puede configurar automáticamente la FPGA en un evento de encendido o reinicio posterior según lo determinado por la configuración del puente de modo (ver Figura 3). Los archivos de programación almacenados en el dispositivo flash permanecerán hasta que se sobrescriban, independientemente de los eventos del ciclo de energía.

La programación de la flash puede tardar entre cuatro y cinco minutos, lo que se debe principalmente al largo proceso de borrado inherente a la tecnología de memoria. Sin embargo, una vez escrita, la configuración de la FPGA puede ser muy rápida, menos de un segundo. La compresión de bitstream, el ancho del bus SPI y la velocidad de configuración son factores controlados por las herramientas de Xilinx que pueden afectar la velocidad de configuración. La Arty admite anchos de bus x1, x2 y x4 y velocidades de datos de hasta 50 MHz para la programación Quad-SPI.

La programación Quad-SPI se puede realizar usando el administrador de hardware en Vivado o con la herramienta iMPACT incluida con ISE.

Memoria

La placa Arty contiene dos memorias externas: una SDRAM DDR3L de 256MB y un dispositivo flash serial no volátil de 128Mb (16MB). El módulo DDR3L está conectado a la FPGA usando la interfaz estándar de la industria. La flash serial está en un bus SPI dedicado de modo cuádruple (x4). La conexión y la asignación de pines entre la FPGA y las memorias externas se muestran a continuación.

DDR3L

La Arty incluye un componente de memoria MT41K128M16JT-125, creando una única interfaz de rango, de 16 bits de ancho. Se enruta a un banco FPGA HR (High Range) alimentado con 1.35V con una impedancia de traza de extremo único controlada de 50 ohmios. Se utilizan terminaciones internas de 50 ohmios en la FPGA para que coincidan con las características de la traza. De manera similar, en el lado de la memoria, se utilizan terminaciones en el chip (ODT) para la adaptación de impedancia.

Para el correcto funcionamiento de la memoria, es necesario incluir un controlador de memoria y una interfaz de capa física (PHY) en el diseño de la FPGA. La forma más fácil de lograr esto en la Arty es usar el núcleo de soluciones de interfaz de memoria de la serie 7 de Xilinx generado por el Asistente MIG (Memory Interface Generator). Dependiendo de la herramienta utilizada (ISE, EDK o Vivado), el Asistente MIG puede generar un estilo FIFO nativo o una interfaz AXI4 para conectarse a la lógica del usuario. Este flujo de trabajo permite la personalización de varios parámetros DDR optimizados para la aplicación particular. La Tabla 2 a continuación enumera la configuración del Asistente MIG optimizada para la Arty.

| Ajuste | Valor |

| Tipo de memoria | DDR3 SDRAM |

| Período máximo de reloj | 3000ps (tasa de datos de 667Mbps) |

| Parte de la memoria | MT41K128M16XX-15E |

| Voltaje de la memoria | 1.35V |

| Ancho de datos | 16 |

| Máscara de datos | Activado |

| Período de reloj de entrada recomendado | 6000ps (166.667 MHz) |

| Control de impedancia del controlador de salida | RZQ/6 |

| Pin de selección de chip del controlador | Activado |

| Rtt (nominal) – terminación en el chip | RZQ/6 |

| Intervalo Vref | Activado |

| Impedancia de terminación interna | 50omhs |

Tabla 3. Configuración DDR3L para la Arty.

El Asistente MIG requerirá que se ingrese y valide la distribución de pines fija de las señales de memoria antes de generar el núcleo IP. Para su comodidad, se proporciona un archivo UCF importable en el centro de recursos de Arty para acelerar este proceso. Se incluye en la descarga del recurso de diseño "MIG Project". Esta descarga también incluye un archivo .prj que se puede importar al asistente para configurarlo automáticamente con las opciones que se encuentran en la Tabla 2.

Para obtener más detalles sobre el Xilinx MIG, consulte la Guía del usuario de soluciones de interfaz de memoria de FPGA de la serie 7 (ug586).

Flash Quad-SPI

Los archivos de configuración de la FPGA se pueden escribir en la flash Quad-SPI (número de pieza de Micron N25Q128A13ESF40), y configurar el puente de modo hará que la FPGA lea automáticamente una configuración de este dispositivo al encenderse. Un archivo de configuración Artix-7 35T requiere 17.536.096 bits de memoria, dejando alrededor del 87% del dispositivo flash (o ~14MB) disponible para los datos del usuario. Un uso común para esta memoria adicional es almacenar programas MicroBlaze demasiado grandes para caber en la memoria de bloque integrada (típicamente 128 KB). Estos programas se cargan y ejecutan usando un programa de cargador de arranque más pequeño que puede caber en la memoria de bloque. Es posible generar automáticamente este cargador de arranque, incluirlo en un solo archivo (llamado archivo .mcs) que también contiene el bitstream y su aplicación MicroBlaze personalizada, y programar este archivo en la flash SPI usando Xilinx SDK y Vivado. Xilinx Answer Record 63605 explica cómo hacer esto.

El contenido de la memoria se puede manipular emitiendo ciertos comandos en el bus SPI. La implementación de este protocolo está fuera del alcance de este documento. Todas las señales en el bus SPI son pines de E/S de usuario de propósito general después de la configuración de la FPGA. En otras placas, SCK es una excepción porque sigue siendo un pin dedicado incluso después de la configuración, sin embargo, en Arty la señal SCK se enruta a un pin de propósito general adicional al que se puede acceder después de la configuración (ver la Figura a continuación). Esto permite el acceso a este pin sin tener que instanciar la primitiva FPGA especial llamada STARTUPE2.

El núcleo AXI Quad SPI de Xilinx se puede usar para leer/escribir la flash en un diseño MicroBlaze. Consulte la guía de productos de Xilinx para este núcleo para obtener más información sobre su uso, o la hoja de datos de Micron para el dispositivo flash para aprender cómo implementar un controlador personalizado.

Ethernet PHY

La Arty incluye un Ethernet PHY 10/100 de Texas Instruments (número de pieza de TI DP83848J) emparejado con un conector Ethernet RJ-45 con magnéticos y LED indicadores integrados. El TI PHY usa la interfaz MII y soporta 10/100 Mb/s. La Figura 5 ilustra las conexiones de pines entre el Artix-7 y el Ethernet PHY. En el reinicio al encenderse, el PHY se establece en los siguientes valores predeterminados:

- Interfaz de modo MII

- Autonegociación habilitada, anunciando todos los modos 10/100 compatibles

- Dirección PHY=00001

- Modo LED 2

Dos LED que se encuentran en el conector Ethernet (J9) están conectados al PHY para proporcionar retroalimentación sobre el estado del enlace y la actividad de los datos. Consulte la hoja de datos del PHY para obtener más detalles. Tenga en cuenta que es normal que un LED esté iluminado y otro apagado, incluso cuando no se usa el Ethernet PHY.

Los diseños basados en Vivado IPI pueden acceder al PHY usando el núcleo IP AXI EthernetLite, el núcleo IP AXI 1G/2.5G Ethernet Subsystem o el núcleo IP Tri Mode Ethernet MAC. Es necesario generar un reloj de 25 MHz para el pin X1 del PHY externo, etiquetado como ETH_REF_CLK en el esquema de Arty. Para aprender cómo usar correctamente el Ethernet PHY en un diseño MicroBlaze en la Arty, consulte el tutorial Getting Started with MicroBlaze Servers del Centro de recursos de Arty.

Para obtener más información sobre el Ethernet PHY, consulte la hoja de datos DP83848J.

Osciladores/Relojes

La placa Arty incluye un único oscilador de cristal de 100 MHz conectado al pin E3 (E3 es una entrada MRCC en el banco 35). El reloj de entrada puede controlar MMCM o PLL para generar relojes de varias frecuencias y con relaciones de fase conocidas que pueden ser necesarias en todo el diseño. Algunas reglas restringen qué MMCM y PLL pueden ser controlados por el reloj de entrada de 100 MHz. Para una descripción completa de estas reglas y de las capacidades de los recursos de reloj de Artix-7, consulte la "Guía del usuario de recursos de reloj de FPGA de la serie 7" disponible en Xilinx.

Xilinx ofrece el núcleo IP Clocking Wizard para ayudar a los usuarios a generar los diferentes relojes necesarios para un diseño específico. Este asistente instanciará correctamente los MMCM y PLL necesarios en función de las frecuencias deseadas y las relaciones de fase especificadas por el usuario. A continuación, el asistente generará un componente contenedor fácil de usar alrededor de estos recursos de reloj que se puede insertar en el diseño del usuario. Se puede acceder al asistente de reloj desde las herramientas Project Navigator o Core Generator.

Puente USB-UART (Puerto serie)

La Arty incluye un puente USB-UART FTDI FT2232HQ (conectado al conector J10) que le permite usar aplicaciones de PC para comunicarse con la placa usando los comandos estándar del puerto COM de Windows. Los controladores de puerto USB-COM gratuitos, disponibles en www.ftdichip.com bajo el encabezado "Virtual Com Port" o VCP, convierten los paquetes USB en datos de puerto serie/UART. Los datos del puerto serie se intercambian con la FPGA usando un puerto serie de dos cables (TXD/RXD). Después de instalar los controladores, se pueden usar comandos de E/S desde el PC dirigidos al puerto COM para producir tráfico de datos serie en los pines A9 y D10 de la FPGA.

Dos LED de estado integrados proporcionan retroalimentación visual sobre el tráfico que fluye a través del puerto: el LED de transmisión (LD10) y el LED de recepción (LD9). Los nombres de las señales que implican la dirección son desde el punto de vista del DTE (Equipo de terminación de datos), en este caso el PC.

El FT2232HQ también se usa como controlador para el circuito Digilent USB-JTAG, pero las funciones USB-UART y USB-JTAG se comportan de forma totalmente independiente entre sí. Los programadores interesados en usar la funcionalidad UART del FT2232 dentro de su diseño no necesitan preocuparse de que el circuito JTAG interfiera con las transferencias de datos UART, y viceversa. La combinación de estas dos características en un solo dispositivo permite que la Arty se programe, se comunique a través de UART y se alimente desde un ordenador conectado con un solo cable Micro USB.

La señal CK_RST (ver el esquema de Arty) también está conectada al dispositivo FT2232HQ a través de JP2. Cuando JP2 está en cortocircuito, el FT2232HQ puede activar un reinicio de MicroBlaze, imitando el comportamiento de las placas Arduino y chipKIT cuando se cargan los bocetos. Tenga en cuenta que la señal CK_RST también está conectada al botón RESET rojo y al pin RST de J7 en el conector del blindaje (estas conexiones no se muestran en la figura a continuación).

Las conexiones entre el FT2232HQ y el Artix-7 se muestran en la Figura 6.

E/S básicas

La placa Arty incluye cuatro LED tricolor, 4 interruptores, 4 pulsadores, 4 LED individuales y un botón de reinicio, como se muestra en la Figura 16. Los pulsadores y los interruptores deslizantes están conectados a la FPGA a través de resistencias en serie para evitar daños por cortocircuitos involuntarios (podría producirse un cortocircuito si un pin de la FPGA asignado a un pulsador o interruptor deslizante se definiera inadvertidamente como una salida). Los cuatro pulsadores son interruptores "momentáneos" que normalmente generan una salida baja cuando están en reposo, y una salida alta solo cuando se pulsan. Los interruptores deslizantes generan entradas altas o bajas constantes en función de su posición.

El botón rojo de reinicio etiquetado como "RESET" genera una salida alta cuando está en reposo y una salida baja cuando se pulsa. El botón

RESET está diseñado para utilizarse en diseños MicroBlaze para reiniciar el procesador, pero también puede utilizarlo como un pulsador de propósito general. Tenga en cuenta que también está conectado al pin RST en J7 del conector de blindaje y al dispositivo UART FT2232 a través de JP2, aunque estas conexiones no se muestran en la figura siguiente.

Los cuatro LED individuales de alta eficiencia están conectados por el ánodo a la FPGA a través de resistencias de 330 ohmios, por lo que se encenderán cuando se aplique un voltaje alto lógico a su respectivo pin de E/S. Los LED adicionales que no son accesibles para el usuario indican el encendido, el estado de programación de la FPGA y el estado de los puertos USB y Ethernet.

LED tricolor

La placa Arty contiene cuatro LED tricolor. Cada LED tricolor tiene tres señales de entrada que controlan los cátodos de tres LED internos más pequeños: uno rojo, uno azul y uno verde. Si se activa la señal correspondiente a uno de estos colores, se iluminará el LED interno. Las señales de entrada son controladas por la FPGA a través de un transistor, que invierte las señales. Por lo tanto, para encender el LED tricolor, las señales correspondientes deben ser activadas en alto. El LED tricolor emitirá un color dependiente de la combinación de LED internos que estén actualmente iluminados. Por ejemplo, si las señales roja y azul se activan en alto y la verde se activa en bajo, el LED tricolor emitirá un color púrpura.

Nota: Digilent recomienda encarecidamente el uso de la modulación por ancho de pulsos (PWM) al controlar los LED tricolor. Si se acciona cualquiera de las entradas a un nivel lógico '1' constante, el LED se iluminará a un nivel incómodamente brillante. Puede evitarlo asegurándose de que ninguna de las señales tricolor se controle con un ciclo de trabajo superior al 50%. El uso de PWM también amplía enormemente la paleta de colores potenciales del LED tricolor. El ajuste individual del ciclo de trabajo de cada color entre el 50% y el 0% hace que los diferentes colores se iluminen con diferentes intensidades, lo que permite mostrar prácticamente cualquier color.

Conectores Pmod

Los conectores Pmod son conectores hembra de 2×6, en ángulo recto, espaciados 100-mil que se acoplan con cabezales de clavija estándar de 2×6. Cada conector Pmod de 12 clavijas proporciona dos señales VCC de 3,3 V (clavijas 6 y 12), dos señales de tierra (clavijas 5 y 11) y ocho señales lógicas, como se muestra en la Fig. 16. Las clavijas VCC y de tierra pueden suministrar hasta 1 A de corriente, pero se debe tener cuidado de no exceder ninguno de los presupuestos de energía de los reguladores integrados o de la fuente de alimentación externa (estos se describen en la sección "Fuentes de alimentación").

Digilent produce una gran colección de placas accesorias Pmod que se pueden conectar a los conectores de expansión Pmod para añadir funciones prefabricadas como A/D, D/A, controladores de motor, sensores y otras funciones.

El Arty tiene cuatro conectores Pmod, algunos de los cuales se comportan de forma diferente a los demás. Cada conector Pmod se incluye en una de las dos categorías: estándar o de alta velocidad. La Tabla 9 especifica en qué categoría se incluye cada Pmod, y también enumera los pines de la FPGA a los que están conectados. Las siguientes secciones describen los diferentes tipos de Pmod.

| Pmod JA | Pmod JB | Pmod JC | Pmod JD | |

| Tipo de Pmod | Estándar | Alta velocidad | Alta velocidad | Estándar |

| Clavija 1 | G13 | E15 | U12 | D4 |

| Clavija 2 | B11 | E16 | V12 | D3 |

| Clavija 3 | A11 | D15 | V10 | F4 |

| Clavija 4 | D12 | C15 | V11 | F3 |

| Clavija 7 | D13 | J17 | U14 | E2 |

| Clavija 8 | B18 | J18 | V14 | D2 |

| Clavija 9 | A18 | K15 | T13 | H2 |

| Clavija 10 | K16 | J15 | U13 | G2 |

Tabla 4. Categorías de conectores Pmod.

Pmod estándar

Los conectores Pmod estándar están conectados a la FPGA a través de resistencias en serie de 200 ohmios. Las resistencias en serie evitan los cortocircuitos que pueden producirse si el usuario acciona accidentalmente una señal que se supone que debe utilizarse como entrada. La desventaja de esta protección añadida es que estas resistencias pueden limitar la velocidad máxima de conmutación de las señales de datos. Si el Pmod que se utiliza no requiere un acceso de alta velocidad, entonces se debe utilizar el conector Pmod estándar para ayudar a prevenir daños a los dispositivos.

Pmod de alta velocidad

Los Pmod de alta velocidad utilizan el conector Pmod estándar, pero tienen sus señales de datos enrutadas como pares diferenciales de impedancia adaptada para obtener la máxima velocidad de conmutación. Tienen almohadillas para cargar resistencias para una mayor protección, pero el Arty se envía con estas cargadas como derivaciones de 0 ohmios. Con las resistencias en serie desviadas, estos Pmod no ofrecen ninguna protección contra cortocircuitos, pero permiten velocidades de conmutación mucho más rápidas. Las señales están emparejadas con las señales adyacentes en la misma fila: clavijas 1 y 2, clavijas 3 y 4, clavijas 7 y 8, y clavijas 9 y 10.

Las trazas se enrutan a 100 ohmios (+/- 10%) diferenciales.

Estos conectores deben utilizarse solo cuando se requiera señalización diferencial de alta velocidad o cuando todos los demás Pmod estén ocupados. Si se utilizan como single-ended, los pares acoplados pueden tener una diafonía significativa. En las aplicaciones en las que esto sea una preocupación, se utilizará el conector Pmod estándar. Otra opción sería conectar a tierra una de las señales (accionarla en bajo desde la FPGA) y utilizar su par para la señal single-ended.

Dado que los Pmod de alta velocidad tienen derivaciones de 0 ohmios en lugar de resistencias de protección, el operador debe tomar precauciones para asegurarse de que no causan ningún cortocircuito.

Conector de shield Arduino/chipKIT

Arty se puede conectar a shields estándar de Arduino y chipKIT para añadir funcionalidad extendida. Se tuvo especial cuidado al diseñar Arty para asegurar que es compatible con la mayoría de los shields de Arduino y chipKIT en el mercado. El conector de shield tiene 49 pines conectados al FPGA para E/S Digitales de propósito general. Debido a la flexibilidad de los FPGA, es posible utilizar estos pines para casi cualquier cosa, incluyendo lectura/escritura digital, conexiones SPI, conexiones UART, conexiones I2C y PWM. Seis de estos pines (etiquetados AN0-AN5) también se pueden utilizar como entradas analógicas de un solo extremo con un rango de entrada de 0V-3.3V, y otros seis (etiquetados AN6-11) se pueden utilizar como entradas analógicas diferenciales.

Nota: Arty no es compatible con shields que emiten señales digitales o analógicas de 5V. Alimentar los pines en el conector de shield de Arty por encima de 5V puede causar daños al FPGA.

La siguiente figura muestra los pines que se encuentran en el conector de shield de Arty.

| Nombre del pin | Función del shield | Conexión Arty |

| IO0-IO13, IO26-IO41, A (IO42) | Pines de E/S de propósito general | Ver la sección titulada "E/S Digital del Shield" |

| SCL | Reloj I2C | Ver la sección titulada "E/S Digital del Shield" |

| SDA | Datos I2C | Ver la sección titulada "E/S Digital del Shield" |

| SCLK | Reloj SPI | Ver la sección titulada "E/S Digital del Shield" |

| MOSI | Salida de datos SPI | Ver la sección titulada "E/S Digital del Shield" |

| MISO | Entrada de datos SPI | Ver la sección titulada "E/S Digital del Shield" |

| SS | Selección de esclavo SPI | Ver la sección titulada "E/S Digital del Shield" |

| A0-A5 | Entrada analógica de un solo extremo | Ver la sección titulada "E/S Digital del Shield" |

| A6-A11 | Entrada analógica diferencial | Ver la sección titulada "E/S Digital del Shield" |

| V_P, V_N | Analógico diferencial dedicado | Ver la sección titulada "E/S Digital del Shield" |

| XGND | tierra analógica XADC de entrada | Conectado a la red utilizada para controlar la referencia de tierra XADC en el FPGA (VREFN) |

| XVREF | Voltaje analógico XADC | Conectado a un riel de 1.25V, 25mA utilizado para controlar la referencia de voltaje XADC en el FPGA (VREFP) |

| N/C | No conectado | No conectado |

| IOREF | Referencia de voltaje de E/S Digital | Conectado al riel de alimentación de 3.3V de Arty (ver la sección "Fuentes de alimentación") |

| RST | Restablecer al shield | Conectado al botón rojo "RESET" y a una E/S digital del FPGA. Cuando JP2 está en cortocircuito, también está conectado a la señal DTR del puente FTDI USB-UART. |

| 3V3 | Riel de alimentación de 3.3V | Conectado al riel de alimentación de 3.3V de Arty (ver la sección "Fuentes de alimentación") |

| 5V0 | Riel de alimentación de 5.0V | Conectado al riel de alimentación de 5.0V de Arty (ver la sección "Fuentes de alimentación") |

| GND, G | Tierra | Conectado al plano de tierra de Arty |

| VIN | Entrada de alimentación | Conectado en paralelo con el conector de fuente de alimentación externa (J12). Consulte la sección "Fuentes de alimentación" para obtener información sobre cómo alimentar Arty desde este pin. |

Tabla 5. Tabla de conexión del shield y descripción funcional.

E/S Digital del Shield

Los pines conectados directamente al FPGA se pueden utilizar como entradas o salidas de propósito general. Estos pines incluyen los pines I2C, SPI y de E/S de propósito general. Hay resistencias en serie de 200 ohmios entre el FPGA y los pines de E/S digitales para ayudar a proporcionar protección contra cortocircuitos accidentales. Los voltajes de funcionamiento máximo absoluto y recomendado para estos pines se describen en la tabla a continuación.

| Voltaje mínimo absoluto | Voltaje de funcionamiento mínimo recomendado | Voltaje de funcionamiento máximo recomendado | Voltaje máximo absoluto | |

| Alimentado | -0.4V | -0.2V | 3.4V | 3.75V |

| Sin alimentación | -0.4V | N/A | N/A | 0.55V |

Tabla 6. Voltajes de funcionamiento máximo absoluto y recomendado.

Para obtener más información sobre las características eléctricas de los pines conectados al FPGA, consulte lahoja de datosdeArtix-7deXilinx.

E/S Analógica del Shield

Los pines etiquetados A0-A11 y V_P/V_N se utilizan como entradas analógicas al módulo XADC del FPGA. El FPGA espera que las entradas tengan un rango de 0-1 V. En los pines etiquetados A0-A5 utilizamos un circuito externo para reducir el voltaje de entrada desde 3.3V. Este circuito se muestra en la Figura 11.2.1. Este circuito permite que el módulo XADC mida con precisión cualquier voltaje entre 0V y 3.3V (en relación con la GND de Arty) que se aplique a cualquiera de estos pines. Si desea utilizar los pines etiquetados A0-A5 como entradas o salidas digitales, también están conectados directamente al FPGA antes del circuito divisor de resistencia (también se muestra en la Figura 11.2.1).

Los pines etiquetados A6-A11 están conectados directamente a 3 pares de pines con capacidad analógica en el FPGA a través de un filtro anti-aliasing. Este circuito se muestra en la Figura 11.2.2. Estos pares de pines se pueden utilizar como entradas analógicas diferenciales con una diferencia de voltaje entre 0-1V. Los números pares están conectados a los pines positivos del par y los números impares están conectados a los pines negativos (por lo que A6 y A7 forman un par de entrada analógica con A6 siendo positivo y A7 siendo negativo). Tenga en cuenta que aunque los pads para el capacitor están presentes, no están cargados para estos pines. Dado que los pines con capacidad analógica del FPGA también se pueden utilizar como pines FPGA digitales normales, también es posible utilizar estos pines para E/S Digital.

Los pines etiquetados V_P y V_N están conectados a las entradas analógicas dedicadas VP_0 y VN_0 del FPGA. Este par de pines también se puede utilizar como una entrada analógica diferencial con voltaje entre 0-1V, pero no se pueden utilizar como E/S Digital. El capacitor en el circuito que se muestra en la Figura 11.2.2 para este par de pines está cargado en el Arty.

El núcleo XADC dentro del Artix-7 es un convertidor analógico-digital de doble canal de 12 bits capaz de operar a 1 MSPS. Cualquiera de los canales puede ser controlado por cualquiera de las entradas analógicas conectadas a los pines del shield. El núcleo XADC se controla y se accede desde un diseño de usuario a través del puerto de reconfiguración dinámica (DRP). El DRP también proporciona acceso a los monitores de voltaje que están presentes en cada uno de los rieles de alimentación del FPGA, y un sensor de temperatura que es interno al FPGA. Para obtener más información sobre el uso del núcleo XADC, consulte el documento de Xilinx titulado 7 Series FPGAs and Zynq-7000 All Programmable SoC XADC Dual 12-Bit 1 MSPS Analog-to-Digital Converter. Una demostración que utiliza el núcleo XADC está disponible en el centro de recursos de Arty.

Referencias

Descargar el manual

Aquí puede descargar la versión PDF completa del manual. Puede contener instrucciones de seguridad adicionales, información de garantía, reglas de la FCC, etc.

Descargar Manual de Arty de Digilent